LICZNIKI

LICZNIKI

LICZNIKI

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

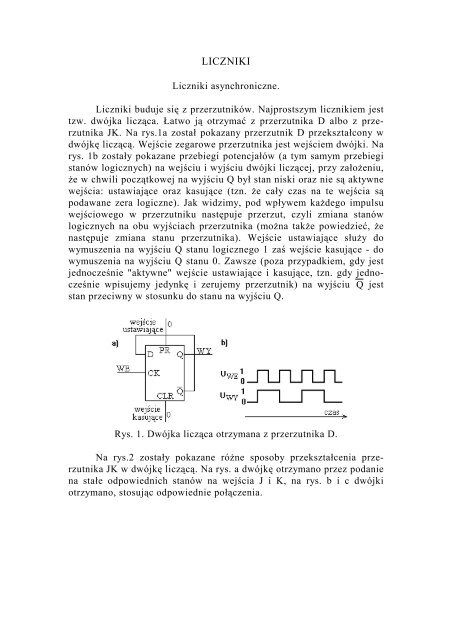

Ćwiczenie "Liczniki" strona 3Rys. 4. Schemat licznika liczącego mod. 4, zbudowanego z dwu dwójekliczących otrzymanych z przerzutników JK z zaprzeczonymi wejściamizegarowymi.Jak łatwo się zorientować, połączone trzy dwójki liczące dadząlicznik liczący mod. 8, cztery dwójki dadzą licznik liczący mod. 16 itd.Tak budowane liczniki nazywane są licznikami asynchronicznymi, gdyŜzmiana stanu danej dwójki liczącej zachodzi jako konsekwencja uprzedniejzmiany stanu na wyjściu poprzedniej dwójki. Zmiana stanu dwójkinastępnej zachodzi później, niŜ zmiana stanu dwójki poprzedniej. Opóźnieniate wynikają z tego, Ŝe pomiędzy momentami zmian stanu nawejściu i na wyjściu przerzutnika danego przerzutnika upływa pewienczas, tzw. "czas propagacji" sygnału przez przerzutnik. Jest to czaszwiązany głównie z ładowaniem pojemności elektrod wewnętrznychprzerzutnika przez oporności jego elementów składowych.MoŜliwe jest zbudowanie z trzech dwójek liczących licznika liczącegonp. "do pięciu" albo "do sześciu", czy teŜ z czterech dwójeklicznika liczącego np. "do dziesięciu". Trzeba w tym celu zmusićwszystkie dwójki do "wyzerowania się" w momencie, gdy zawartośćlicznika osiągnie odpowiednią wartość - wartość 5, gdy ma liczyć "dopięciu", wartość 6, gdy ma liczyć "do sześciu", wartość 10, gdy maliczyć "do dziesięciu". Do tego celu słuŜą wejścia zerujące przerzutników.Potrzebny jest tylko układ "wykrywający" daną liczbę na wyjściulicznika i wysyłający impuls zerujący przerzutniki. Układ wykrywającydaną liczbę buduje się z bramek.Aby ułatwić budowę liczników pracujących w układach dziesiętnychoraz odmierzających czas (potrzebne tu np.liczenie "do 6"), zostałyzaprojektowane specjalne podzespoły w postaci układów scalonych, liczącychmod. 2 i mod. 5 (UCY 7490), mod. 2 i mod. 6 (UCY7492) orazmod. 2 i mod. 8 (UCY7493). Licznik liczący mod 10 łatwo jest uzyskaćz układu 7490 albo 7493. Licznik liczący mod. 60 uzyskamy łącząc np.licznik mod. 10 z licznikiem mod. 6. Rysunek 5a przedstawia schematlogiczny licznika scalonego UCY7493. Trzy dwójki liczące w tym podzespolesą ze sobą na stałe połączone wewnątrz układu w ten sposób, Ŝewejście dwójki następnej jest połączone z wyjściem dwójki poprzedniej.Połączone ze sobą są wejścia kasujące (zerujące) wszystkich dwójek.

Ćwiczenie "Liczniki" strona 4Kółeczka przy tych wejściach oznaczają, Ŝe są to wejścia "zanegowane".Gdy na takim wejściu istnieje zero logiczne, to na wyjściu Q jest wymuszonystan niski. Dostęp do wejść zerujących prowadzi przez dwuwejściowąbramkę NAND. Jeśli na oba wejścia tej bramki (wyprowadzenia onumerach 2 i 3) są podane stany wysokie (tzn.jedynki logiczne), to licznikUCY7493 nie liczy (jest zerowany). Dzięki takiemu rozwiązaniu jestbardzo łatwo z układu UCY7493 uzyskać np. licznik mod. 10 - wystarczywykonać dwa połączenia (oprócz połączenia wyjścia A z wejściem B).Na rys. 5b widzimy licznik mod. 10 uzyskany z układu UCY7493.Wejścia oraz wyjścia kolejnych dwójek liczących oznacza się kolejnymiliterami alfabetu: WE A, WY A, WE B, WY B, WY C, WY D.a) b)WE WY WY WY WYA A D GND B C14 13 12 11 10 9 8WE1413WYA12WYD11GNDWYB9WYC8K Q K Q K Q K QCK CK CK CKJCLR JCLR JCLR JCLRK Q K Q K Q K QCK CK CK CKJCLR JCLR JCLR JCLR7493 74931 2 3 4 5 6 7 1 2 3 4 VCC6 7WE R VB 0(1) R 0(2) CCRys. 5. Schemat logiczny układu UCY7493 (rys. a) i licznik mod. 10zbudowany z układu UCY7493.Na rys. 6a widzimy schemat licznika dziesiętnego UCY7490, zawierającegodwójkę liczącą oraz zespół trzech przerzutników, liczącymod. 5. Wyprowadzenia o numerach 2 i 3 słuŜą do zerowania zawartościlicznika, wyprowadzenia o numerach 6 i 7 słuŜą do wpisywania dolicznika liczby 9. Jeśli wyjście zespołu liczącego do pięciu połączymy zwejściem A (wtedy wejściem licznika będzie wejście B), to otrzymamylicznik liczący do dziesięciu z symetryczną falą sygnału na wyjściu. Zukładów UCY7490 a takŜe UCY7493 bardzo łatwo jest budować licznikidekadowe. Wystarczy połączyć ze sobą szeregowo wymaganą ilośćukładów liczących mod. 10, łącząc wyjście ostatniego przerzutnika danegoukładu scalonego łączymy z wejściem pierwszego przerzutnikanastępnego układu, aby otrzymać Ŝądany licznik. Łącząc dwa układyotrzymujemy licznik mod. 100, łącząc trzy - otrzymujemy licznik mod.1000 itd. KaŜdy układ scalony jest tu dekadą liczącą mod. 10 i podającąwynik w kodzie BCD.

Ćwiczenie "Liczniki" strona 5Na rys. 6b został pokazany schemat wyprowadzeń układu scalonegoUCY7492, stanowiącego licznik mod. 12. Z oznaczeń wyprowadzeńukładu moŜna wywnioskować, Ŝe zawiera on dwójką liczącą orazzespół przerzutników liczący mod. 6.a)WEA14JCPKA13WYAJ12CPKBWYD11JCPKGND10CWYB9S1S2RWYC8DCPS D74901 2 3 4 5 6 71 2 3 4 5 6 7 WE V R RWE R0(1) R0(2)VCCR9(1) RBCC 0(1) 0(2)9(2)BRys. 6. Schemat budowy układu UCY7490 oraz schemat wyprowadzeńukładu UCY7492.b)WEA Q Q GND Q Q14 13 12 11 10 9 8ABA B C DQ AQ BQ7492Cechą ujemną liczników asynchronicznych jest generowanie przeznie fałszywych liczb na wyjściu licznika z powodu nierównoczesnego(coraz późniejszego) występowania zboczy impulsów na wyjściachkolejnych przerzutników. Szybki dekoder liczb pośredniczący pomiędzytakim licznikiem a jakimś innym urządzeniem będzie podawał do tegourządzenia fałszywe liczby. Na przykład po przyjściu na wejście układuUCY7493 ósmego impulsu pojawią się na wyjściu licznika pomiędzyprawidłowymi liczbami: "0111" (siedem) i "1000" (osiem) trzy fałszyweliczby: "0110" (sześć), "0100" (cztery) i "0000" (zero). Rysunek 7ilustruje przyczynę występowania tego zjawiska.RRQ CD0(2)0(1)Rys. 7. Powstawanie fałszywych liczb na wyjściu licznikaasynchronicznego

Ćwiczenie "Liczniki" strona 6Liczniki synchroniczne.W liczniku synchronicznym ten sam sygnał wejściowy (zliczaneimpulsy) jest jednocześnie podawany na wejścia zegarowe wszystkichprzerzutników. Na wejścia J i K pierwszego przerzutnika (przerzutnikoznaczony literą A na rys. 8) są podane "na stałe" jedynki logiczne. Podwpływem kaŜdego impulsu wejściowego w przerzutniku tym następujezmiana stanu przerzutnika. Inaczej jest z przerzutnikami następnymi. Nawejścia J i K drugiego przerzutnika jest podawany stan z wyjściapierwszego przerzutnika. Na wejścia J i K kaŜdego następnego przerzutnikajest podawany iloczyn logiczny stanów wyjść wszystkichpoprzednich przerzutników. Jeśli na wyjściu pierwszego przerzutnikaistnieje stan niski, to stan przerzutnika drugiego nie się zmieni się; jeślina wyjściu pierwszego przerzutnika istnieje stan wysoki, to stan przerzutnikadrugiego zmieni się pod wpływem impulsu podawanego na jegowejście zegarowe. Jeśli iloczyn logiczny stanów wyjść wszystkichprzerzutników poprzedzających dany przerzutnik ma wartość "1", to standanego przerzutnika zmieni się, jeśli wartość tego iloczynu wynosi "0",to stan danego przerzutnika nie zmieni się. Tak więc, gdy np. nawyjściach przerzutników A i B są stany wysokie, to pod wpływem zboczaopadającego impulsu na wejściu licznika nastąpi przerzut w przerzutnikuC.Jeśli w rozpatrywanym liczniku pod wpływem impulsu wejściowegonastępują zmiany stanu kilku przerzutników, to następują one wtym samym momencie. Dlatego teŜ licznik taki nazywa się licznikiemsynchronicznym. Do bramek podających sygnał na połączone wejścia J iK przerzutników są doprowadzone przewody z wyjść wszystkich poprzednichprzerzutników. Taki licznik nosi nazwę licznika synchronicznegoz przeniesieniami równoległymi.Rys. 8. Licznik synchroniczny z przeniesieniami równoległymi.

Ćwiczenie "Liczniki" strona 7Na rys. 9 zostały przedstawione przebiegi napięć na wejściach iwyjściach licznika synchronicznego. U dołu - nad osią czasu - zostałyzaznaczone okresy czasu oraz przerzutniki mające w tych okresach podanejedynki logiczne na wejścia J i K, pozwalające na przerzut tychprzerzutników.Rys 9. Zmiany stanów logicznych w liczniku synchronicznym.Rysunek 10 przedstawia licznik synchroniczny z przeniesieniamiszeregowymi. Licznik ten działa na takiej samej zasadzie jak licznik zprzeniesieniami równoległymi, z tym, Ŝe w inny sposób jest uzyskiwanyiloczyn logiczny stanów wyjść przerzutników poprzedzających danyprzerzutnik. Zamiast dla kolejnych przerzutników stosować bramki ocoraz to większej ilości wejść, stosuje się bramki dwuwejściowe. Wtakim rozwiązaniu czas dojścia sygnału z jednego przerzutnika do odległegodrugiego jest równy sumie czasów propagacji sygnału wszystkichprzerzutników, przez które ten sygnał przechodzi. DuŜy czasprzejścia sygnału pomiędzy pierwszym a ostatnim przerzutnikiem silnieogranicza od góry wartość maksymalnej częstości impulsów, które moŜepoprawnie zliczać taki licznik.Rys. 10. Licznik synchroniczny z przeniesieniami szeregowymi.

Ćwiczenie "Liczniki" strona 8Liczniki rewersyjne.W oparciu o zasadę działania liczników synchronicznych, w którychten sam sygnał wejściowy jest doprowadzany do wszystkich przerzutnikówbuduje się liczniki rewersyjne, czyli liczniki mogące liczyć"do przodu" i "do tyłu". W liczniku liczącym normalnie, czyli do przodu,kaŜdy impuls podawany na wejście powoduje zwiększenie o 1 zawartościlicznika; w liczniku liczącym do tyłu kaŜdy impuls podawany nawejście powoduje zmniejszenie o 1 zawartości licznika.Na rys. 11 został przedstawiony licznik rewersyjny zbudowany ztrzech przerzutników JK. Oprócz wejścia dla zliczanych impulsów licznikposiada wejście (WE R) dla określenia kierunku liczenia. LicznikmoŜna rozbudowywać - powiększając układ o dalsze przerzutniki orazstosując dla kaŜdego następnego przerzutnika jedną dwuwejściowąbramkę NAND oraz parę bramek o coraz to większej ilości wejść. Jeślina wejście WE R jest podana jedynka logiczna, to na wyjściach bramek 2i 5 są jedynki logiczne - wtedy układ działa jako znany nam juŜ, liczącydo przodu, licznik synchroniczny z przeniesieniami równoległymi. Jeślina wejściu WE R jest zero logiczne, wtedy stan pierwszego przerzutnika- podobnie jak przy liczeniu do przodu - zmienia się pod wpływemkaŜdego impulsu wejściowego. Jeśli chodzi o dalsze przerzutniki, to -jak moŜna zauwaŜyć - dany przerzutnik moŜe zmienić swój stan podwpływem impulsu wejściowego, gdy na wyjściach Q przerzutnikówpoprzedzających dany przerzutnik są zera logiczne. Taka logika zmianstanów logicznych wyjść poszczególnych przerzutników powoduje Ŝelicznik liczy do tyłu, zmniejszając swoją zawartość.Rys. 11. Licznik rewersyjny z przeniesieniami rónoległymi.Na rys. 12 zostały przedstawione przebiegi napięć na wejściach iwyjściach licznika rewersyjnego przedstawionego na rys. 11. U dołu rys.

Ćwiczenie "Liczniki" strona 912 zostały zaznaczone okresy czasu oraz przerzutniki mające w tychokresach podane jedynki logiczne na wejścia J i K, pozwalające naprzerzut tych przerzutników przy podanym zerze logicznym na wejściuWE R, tzn. gdy licznik liczy do tyłu.Rys.12. Zmiany stanów logicznych w liczniku rewersyjnym liczącym dotyłu.Przedstawiony na rys. 11 licznik rewersyjny posiada przeniesieniarównoległe. W układzie moŜna zastosować takŜe przeniesienia szeregowe,stosując przy dalszych przerzutnikach zamiast bramek NAND ocoraz to większej ilości wejść - trójwejściowe bramki NAND. Na rys. 13został pokazany schemat licznika rewersyjnego z przeniesieniamiszeregowymi.Rys. 13. Licznik rewersyjny z przeniesieniami szeregowymi.Na rys. 14 został pokazany schemat licznika rewersyjnego, posiadającegodwa wejścia dla zliczanych impulsów. Impulsy podawane nawejście "WE P" zwiększają zawartość licznika, impulsy podawane nawejście "WE T" zmniejszają zawartość licznika. Na nieuŜywanym wejściuw tym rozwiązaniu powinien być stan zero. Sygnały z wyjść WY P(wyjście przeniesienia) i WY T (wyjście poŜyczki) moŜna podać nawejścia WE P i WE T następnego, podobnego układu, w celu utworzenia

Ćwiczenie "Liczniki" strona 10licznika rewersyjnego o większej pojemności (całość nie będzie juŜlicznikiem synchronicznym).Rys. 14. Schemat licznika rewersyjnego, posiadającego osobne wejściadla impulsów zwiększajacych i zmniejszających zawartość licznika.Jeśli poszczególne przerzutniki tworzące taki licznik posiadająwejścia zerujące i ustawiające, to do takiego licznika moŜna wpisaćliczbę początkową a potem ją zwiększać albo zmniejszać, podając impulsyna odpowiednie wejścia. Są produkowane liczniki rewersyjne,posiadające wewnętrzne układy wymuszające zerowanie się licznika przyprzekraczaniu zawartości wynoszącej 9 i generujące impuls przeniesienia(albo impuls poŜyczki przy liczeniu do tyłu) oraz posiadające wejścia dowpisania do licznika liczby z zakresu od 0 do 9. Na rys. 15 mamyschemat rozmieszczenia wyprowadzeń układu scalonego UCY74192,będącego takim licznikiem..Rys. 15. Wyprowadzenia licznika rewersyjnego dziesiętnego UCY74192.Znaczenie wyprowadzeń licznika UCY74192.1 - wejście danych B,2 - wyjście B,

Ćwiczenie "Liczniki" strona 113 - wyjście A,4 - wejście dla impulsów posuwających licznik do tyłu,5 - wejście dla impulsów posuwających licznik do przodu,6 - wyjście C,7 - wyjście D,8 - masa,9 - wejście danych D,10 - wejście danych C,11 - wejście dla impulsu wprowadzającego dane do licznika,12 - wyjście przeniesienia,13 - wyjście poŜyczki,14 - wejście dla impulsu zerującego licznik,15 - wejście danych A,16 - dodatni biegun zasilania (+5V).Plan ćwiczenia.1. Zbadać działanie licznika UCY7493.Odrysować wskazania wyświetlacza siedmiosegmentowego, zasilanegoprzez układ scalony UCY7447 (rys.16), sterowany wyjściami A, B, C iD układu UCY7493. Na wejście licznika podawać sygnał TTL oczęstości rzędu 1 Hz.Odrysować z ekranu oscyloskopu przebiegi sygnału na wejściu licznikaoraz na wyjściach A, B, C i D układu scalonego UCY7493. Wskazanejest posługiwać się przystawką dwukanałową dołączoną do oscyloskopudwukanałowego - otrzymamy układ oscyloskopu 3-kanałowego. Zadaniawykonać dla:a) układu liczącego mod. 16,b) układu liczącego mod. 10,c) układu liczącego mod. 7.Uwaga. Pozostawienie wolnych (niepodłączonych gdziekolwiek) wejśćzerujących licznik UCY7493 oznacza podanie na te wejścia stanu wysokiego.Aby licznik liczył mod. 16, naleŜy przynajmniej na jedno wejściezerujące podać stan niski. Dla wykonania punktu c naleŜy zaprojektowaćukład wykrywający liczbę 7 na wyjściu licznika i podający - w momenciewykrycia liczby - jedynki logiczne na oba wejścia zerujące licznika.Otrzymany układ przekształcić tak, by składał się tylko z dwuwejściowychelementów NAND. Do realizacji zadania wystarcza jeden układscalony UCY7400, zawierający 4 dwuwejściowe bramki NAND. Układyscalone wymagają zasilania napięciem stałym o wartości 5V. Numerywyprowadzeń układów, do których doprowadzamy napięcie zasilające sąróŜne dla róŜnych układów; inne dla układów zawierających bramki, innedla układów stanowiących liczniki.Sygnały z wyjść A, B, C i D licznika wprowadzamy na wejścia A,B, C i D układu UCY7447 (rys. 17). Wyjścia a, b, c, d, e, f i g układu

Ćwiczenie "Liczniki" strona 12UCY7447 łączymy - poprzez oporniki ograniczające natęŜenie prądukaŜdego segmentu do wartości 20 mA - z podobnie oznaczonymiwyprowadzeniami siedmiosegmentowego wyświetlacza "LED" posiadającegowspólną anodę wszystkich segmentów. Anodę wyświetlaczałączymy z dodatnią elektrodą zasilacza "+5V". Wejścia transkodera"Lamp Test" i "RB input" (takŜe i "RB output") pozostawiamyniepodłączone. Wyświetlacz wraz z opornikami jest zamontowany naspecjalnej płytce.VCC16B C Lamp RB RB D A GNDTest outputputin-WEJŚCIAWEJŚCIARys. 16. Schemat wyprowadzeń transkodera UCY7447.WYJŚCIAf g a b c d e15 14 13 12 11 10 9f g a b c d eBI/B C LT RBO RBI D A1 2 3 4 5 6 78Rys. 17. Schemat połączenia transkodera UCY7447 oraz wyświetlaczasiedmiosegmentowego LED z licznikiem UCY7493.2. Z trzech przerzutników JK (potrzebne dwa układy scalone UCY7476)oraz układu scalonego UCY7400 zbudować licznik synchroniczny zprzeniesieniami równoległymi liczący mod. 8 (na podst. rys. 8).Potrzebny element AND naleŜy zastąpić równowaŜnym układem zbudowanymz dwu elementów NAND (Jak to zrobić?). Posługując się oscyloskopem,zbadać działanie licznika i przedstawić wykresy zmian stanówlogicznych na wejściu i wyjściu dla 16 impulsów wejściowych.

Ćwiczenie "Liczniki" strona 133. Z czterech przerzutników JK (potrzebne dwa układy scaloneUCY7476) oraz układu scalonego UCY7400 zbudować liczniksynchroniczny z przeniesieniami szeregowymi liczący mod. 16 -wg rys.10). Posługując się oscyloskopem, zbadać działanie licznika iprzedstawić wykresy zmian stanów logicznych na wejściu i wyjściu dla32 impulsów wejściowych.4. Z trzech przerzutników JK (potrzebne dwa układy scalone UCY7476)oraz jednego układu scalonego UCY7400 i jednego układu UCY7410 (3trójwejściowe bramki NAND) zbudować licznik rewersyjny zprzeniesieniami szeregowymi liczący mod. 8 - wg rys.13. Posługując sięoscyloskopem, zbadać działanie licznika i przedstawić wykresy zmianstanów logicznych na wejściu i wyjściu dla 16 impulsów wejściowychdla obu "kierunków" liczenia..5. Posługując się oscyloskopem, zbadać działanie licznika UCY74192.przedstawić przebieg zmian stanów logicznych na wejściu oraz nawszystkich wyjściach licznika dla 20 impulsów zwiększających oraz dla20 impulsów zmniejszających zawartość licznika. Aby licznik liczył,naleŜy na nieuŜywane wejście T podać stan "1", na wejście R - stan "0".Rys. 18. Schemat logiczny układu scalonego UCY7476.Rys. 19. Rozmieszczenie wyprowadzeń w układach scalonych UCY7400i UCY7410.

Ćwiczenie "Liczniki" strona 14LITERATURA1. Jan Pieńkos, Janusz Turczyński: „Układy scalone TTL w systemachcyfrowych”, WKŁ, Warszawa,1980.2. Jan Pieńkos, Janusz Turczyński: „Układy scalone TTL serii UCY74 iich zastosowanie”, WKŁ, Warszawa,1977.3. Andrzej Sowiński:„Cyfrowa technika pomiarowa”, WKŁ, Warszawa,1975.4. Wiesław Traczyk: „Układy cyfrowe automatyki”, Wyd. Naukowo-Techniczne, Warszawa, 1976.5. P. Misiurewicz, M. Grzybek: „Półprzewodnikowe układy logiczneTTL", Wyd. Naukowo - Techniczne. Warszawa, 1979.Roman Kazański,7 czerwca 2001r.Ostatnia zmiana 16 kwietnia 2008r. Plik "oliczn.doc".